FIRST ORDER

FREE 10% DISCOUNT

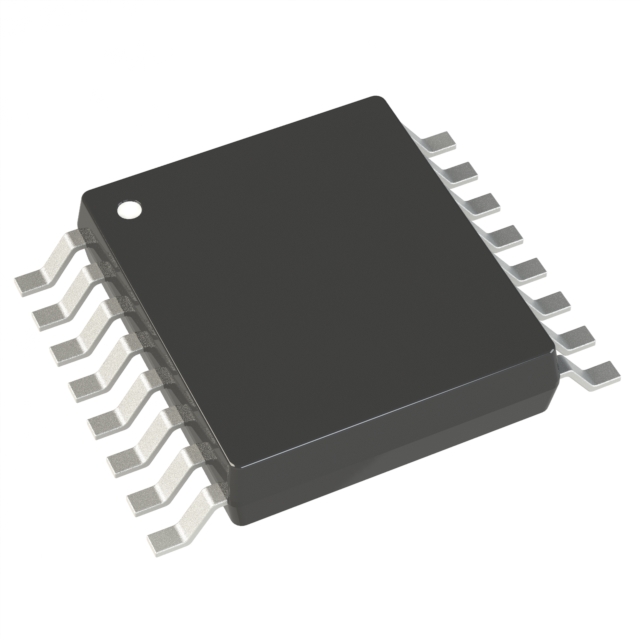

Cyclone® II Field Programmable Gate Array (FPGA) IC 85 165888 8256 144-LQFP

Introduction

Following the immensely successful first-generation Cyclone® device

family, Altera® Cyclone II FPGAs extend the low-cost FPGA density

range to 68,416 logic elements (LEs) and provide up to 622 usable I/O

pins and up to 1.1 Mbits of embedded memory. Cyclone II FPGAs are

manufactured on 300-mm wafers using TSMC's 90-nm low-k dielectric

process to ensure rapid availability and low cost. By minimizing silicon

area, Cyclone II devices can support complex digital systems on a single

chip at a cost that rivals that of ASICs. Unlike other FPGA vendors who

compromise power consumption and performance for low-cost,

Altera’s latest generation of low-cost FPGAs—Cyclone II FPGAs, offer 60%

higher performance and half the power consumption of competing 90-nm FPGAs.

The low cost and optimized feature set of Cyclone II FPGAs make them ideal

solutions for a wide array of automotive, consumer,communications, video processing,

test and measurement, and other end-market solutions. Reference designs,

system diagrams, and IP, found at www.altera.com, are available to help

you rapidly develop complete end-market solutions using Cyclone II FPGAs.

Low-Cost Embedded Processing Solutions

Cyclone II devices support the Nios II embedded processor which allows

you to implement custom-fit embedded processing solutions. Cyclone II

devices can also expand the peripheral set, memory, I/O, or performance

of embedded processors. Single or multiple Nios II embedded processors

can be designed into a Cyclone II device to provide additional

co-processing power or even replace existing embedded processors in

your system. Using Cyclone II and Nios II together allow for low-cost,

high-performance embedded processing solutions, which allow you to

extend your product's life cycle and improve time to market over

standard product solutions.

Low-Cost DSP Solutions

Use Cyclone II FPGAs alone or as DSP co-processors to improve

price-to-performance ratios for digital signal processing (DSP)

applications. You can implement high-performance yet low-cost DSP

systems with the following Cyclone II features and design support:

■ Up to 150 18 × 18 multipliers

■ Up to 1.1 Mbit of on-chip embedded memory

■ High-speed interfaces to external memory

■ DSP intellectual property (IP) cores

■ DSP Builder interface to The Mathworks Simulink and Matlab

design environment

■ DSP Development Kit, Cyclone II Edition

Cyclone II devices include a powerful FPGA feature set optimized for

low-cost applications including a wide range of density, memory,

embedded multiplier, and packaging options. Cyclone II devices

support a wide range of common external memory interfaces and

I/O protocols required in low-cost applications. Parameterizable IP cores

from Altera and partners make using Cyclone II interfaces and protocols fast and easy

Features

The Cyclone II device family offers the following features:

■ High-density architecture with 4,608 to 68,416 LEs

● M4K embedded memory blocks

● Up to 1.1 Mbits of RAM available without reducing available

logic

● 4,096 memory bits per block (4,608 bits per block including 512

parity bits)

● Variable port configurations of ×1, ×2, ×4, ×8, ×9, ×16, ×18, ×32,

and ×36

● True dual-port (one read and one write, two reads, or two

writes) operation for ×1, ×2, ×4, ×8, ×9, ×16, and ×18 modes

● Byte enables for data input masking during writes

● Up to 260-MHz operation

■ Embedded multipliers

● Up to 150 18- × 18-bit multipliers are each configurable as two

independent 9- × 9-bit multipliers with up to 250-MHz

performance

● Optional input and output registers

■ Advanced I/O support

● High-speed differential I/O standard support, including LVDS,

RSDS, mini-LVDS, LVPECL, differential HSTL, and differential

SSTL

● Single-ended I/O standard support, including 2.5-V and 1.8-V,

SSTL class I and II, 1.8-V and 1.5-V HSTL class I and II, 3.3-V PCI

and PCI-X 1.0, 3.3-, 2.5-, 1.8-, and 1.5-V LVCMOS, and 3.3-, 2.5-,

and 1.8-V LVTTL

● Peripheral Component Interconnect Special Interest Group (PCI

SIG) PCI Local Bus Specification, Revision 3.0 compliance for 3.3-V

operation at 33 or 66 MHz for 32- or 64-bit interfaces

● PCI Express with an external TI PHY and an Altera PCI Express

×1 Megacore® function

● 133-MHz PCI-X 1.0 specification compatibility

● High-speed external memory support, including DDR, DDR2,

and SDR SDRAM, and QDRII SRAM supported by drop in

Altera IP MegaCore functions for ease of use

● Three dedicated registers per I/O element (IOE): one input

register, one output register, and one output-enable register

● Programmable bus-hold feature

● Programmable output drive strength feature

● Programmable delays from the pin to the IOE or logic array

● I/O bank grouping for unique VCCIO and/or VREF bank

settings

● MultiVolt™ I/O standard support for 1.5-, 1.8-, 2.5-, and

3.3-interfaces

● Hot-socketing operation support

● Tri-state with weak pull-up on I/O pins before and during

configuration

● Programmable open-drain outputs

● Series on-chip termination support

■ Flexible clock management circuitry

● Hierarchical clock network for up to 402.5-MHz performance

● Up to four PLLs per device provide clock multiplication and

division, phase shifting, programmable duty cycle, and external

clock outputs, allowing system-level clock management and

skew control

● Up to 16 global clock lines in the global clock network that drive

throughout the entire device

■ Device configuration

● Fast serial configuration allows configuration times less than

100 ms

● Decompression feature allows for smaller programming file

storage and faster configuration times

● Supports multiple configuration modes: active serial, passive

serial, and JTAG-based configuration

● Supports configuration through low-cost serial configuration

devices

● Device configuration supports multiple voltages (either 3.3, 2.5,

or 1.8 V)

■ Intellectual property

● Altera megafunction and Altera MegaCore function support,

and Altera Megafunctions Partners Program (AMPPSM)

megafunction support, for a wide range of embedded

processors, on-chip and off-chip interfaces, peripheral

functions, DSP functions, and communications functions and

protocols. Visit the Altera IPMegaStore at www.altera.com to

download IP MegaCore functions.

● Nios II Embedded Processor support

The Cyclone II family offers devices with the Fast-On feature, which

offers a faster power-on-reset (POR) time. Devices that support the

Fast-On feature are designated with an “A” in the device ordering code.For example,

EP2C5A, EP2C8A, EP2C15A, and EP2C20A. The EP2C5A is only available in the automotive speed grade.

The EP2C8A and EP2C20A are only available in the industrial speed grade.

The EP2C15A is only available with the Fast-On feature and is available in both commercial and industrial grades.

The Cyclone II “A” devices are identical in feature set and functionality to the non-A devices except for support of the faster POR time.

Cyclone II A devices are offered in automotive speed grade. For more

information, refer to the Cyclone II section in the Automotive-Grade Device Handbook.

For more information on POR time specifications for Cyclone II A and

non-A devices, refer to the Hot Socketing & Power-On Reset chapter in the Cyclone II Device Handbook.

Table 1–1 lists the Cyclone II device family features. Table 1–2 lists the

Cyclone II device package offerings and maximum user I/O pins.

Chip Altera Cyclone naming rules,Chinese chip Will replace it

Hot Sales

Pricing And ODER

Stock:

0

Price:

$65.57

Quantity:

Shipping Cost

$28.63

PostNL International Mail 11-33

?Unconfirmed payment orders may not be able to deliver the normal cancellation of the order, please communicate with the email to confirm before making the relevant payment ~ Attached email phone number The platform has the right to cancel the unconfirmed payment orders do not need to bear the responsibility of default.

Shipment Date

2025/04/24 PM

Delivery Date

5-10 business days

About Logistics:

?Shipping time will be determined according to the logistics time, there will be differences in the place please understand!

| Sub-Total | $65.57 |

| Shipping: | $28.63 |

| Total | $94.2 |

Please send RFQ , we will respond immediately.

Product:

-

Afghanistan

Afghanistan

-

Afghanistan

Afghanistan

-

Albania

Albania

-

Algeria

Algeria

-

American Samoa

American Samoa

-

Andorra

Andorra

-

Angola

Angola

-

Anguilla

Anguilla

-

Antigua & Barbuda

Antigua & Barbuda

-

Argentina

Argentina

-

Arizona

Arizona

-

Armenia

Armenia

-

Aruba

Aruba

-

Australia

Australia

-

Austria

Austria

-

Azerbaijan

Azerbaijan

-

Bahamas

Bahamas

-

Bahrain

Bahrain

-

Bangladesh

Bangladesh

-

Barbados

Barbados

-

Belarus

Belarus

-

Belgium

Belgium

-

Belize

Belize

-

Benin

Benin

-

Bermuda

Bermuda

-

Bhutan

Bhutan

-

Bolivia

Bolivia

-

Bonaire

Bonaire

-

Bosnia and Herzegovina

Bosnia and Herzegovina

-

Botswana

Botswana

-

Brazil

Brazil

-

British Virgin Islands

British Virgin Islands

-

Brunei

Brunei

-

Bulgaria

Bulgaria

-

Burkina Faso

Burkina Faso

-

Burundi

Burundi

-

California

California

-

Cambodia

Cambodia

-

Cameroon

Cameroon

-

Canada

Canada

-

Cape Verde

Cape Verde

-

Cayman Islands

Cayman Islands

-

Central African Republic

Central African Republic

-

Chad

Chad

-

Chile

Chile

-

Colombia

Colombia

-

Colorado

Colorado

-

Congo

Congo

-

Cook Islands

Cook Islands

-

Costa Rica

Costa Rica

-

Côte d'Ivoire

Côte d'Ivoire

-

Croatia

Croatia

-

Curaçao

Curaçao

-

Curacao

Curacao

-

Cyprus

Cyprus

-

Czech Republic

Czech Republic

-

Democratic Republic of Congo

Democratic Republic of Congo

-

Democratic Republic of the Congo

Democratic Republic of the Congo

-

Denmark

Denmark

-

Djibouti

Djibouti

-

Dominica

Dominica

-

Dominican Republic

Dominican Republic

-

East Timor

East Timor

-

Ecuador

Ecuador

-

Egypt

Egypt

-

El Salvador

El Salvador

-

Eritrea

Eritrea

-

Estonia

Estonia

-

Eswatini

Eswatini

-

Ethiopia

Ethiopia

-

Faroe Islands

Faroe Islands

-

Fiji

Fiji

-

Finland

Finland

-

France

France

-

French Guiana

French Guiana

-

French Polynesia

French Polynesia

-

Gabon

Gabon

-

Gambia

Gambia

-

Georgia

Georgia

-

Germany

Germany

-

Ghana

Ghana

-

Gibraltar

Gibraltar

-

Greece

Greece

-

Greenland

Greenland

-

Grenada

Grenada

-

Guadeloupe

Guadeloupe

-

Guam

Guam

-

Guatemala

Guatemala

-

Guinea

Guinea

-

Guyana

Guyana

-

Haiti

Haiti

-

Honduras

Honduras

-

Hong Kong

Hong Kong

-

Hong Kong, China

Hong Kong, China

-

Hungary

Hungary

-

Iceland

Iceland

-

Idaho

Idaho

-

India

India

-

Indonesia

Indonesia

-

Iraq

Iraq

-

Ireland

Ireland

-

Israel

Israel

-

Italy

Italy

-

Ivory Coast

Ivory Coast

-

Jamaica

Jamaica

-

Japan

Japan

-

Jordan

Jordan

-

Kazakhstan

Kazakhstan

-

Kenya

Kenya

-

Kuwait

Kuwait

-

Kyrgyzstan

Kyrgyzstan

-

Laos

Laos

-

Latvia

Latvia

-

Lebanon

Lebanon

-

Lesotho

Lesotho

-

Liberia

Liberia

-

Libya

Libya

-

Liechtenstein

Liechtenstein

-

Liechtenstein (Switzerland)

Liechtenstein (Switzerland)

-

Lithuania

Lithuania

-

Luxembourg

Luxembourg

-

Macao, China

Macao, China

-

Macau

Macau

-

Macedonia

Macedonia

-

Madagascar

Madagascar

-

Malawi

Malawi

-

Malaysia

Malaysia

-

Maldives

Maldives

-

Mali

Mali

-

Malta

Malta

-

Marshall Islands

Marshall Islands

-

Martinique

Martinique

-

Mauritania

Mauritania

-

Mauritius

Mauritius

-

Mexico

Mexico

-

Micronesia

Micronesia

-

Moldova

Moldova

-

Monaco

Monaco

-

Monaco (France)

Monaco (France)

-

Mongolia

Mongolia

-

Montenegro

Montenegro

-

Montserrat

Montserrat

-

Morocco

Morocco

-

Mozambique

Mozambique

-

Myanmar

Myanmar

-

Namibia

Namibia

-

Nepal

Nepal

-

Netherlands

Netherlands

-

Netherlands Antilles

Netherlands Antilles

-

Nevada

Nevada

-

New Caledonia

New Caledonia

-

New Zealand

New Zealand

-

Nicaragua

Nicaragua

-

Niger

Niger

-

Nigeria

Nigeria

-

North Macedonia

North Macedonia

-

Northern Mariana Islands

Northern Mariana Islands

-

Norway

Norway

-

Oman

Oman

-

Oregon

Oregon

-

Other States in US

Other States in US

-

Pakistan

Pakistan

-

Palau

Palau

-

Palestinian Authority

Palestinian Authority

-

Palestinian Territories

Palestinian Territories

-

Panama

Panama

-

Papua New Guinea

Papua New Guinea

-

Paraguay

Paraguay

-

Peru

Peru

-

Philippines

Philippines

-

Poland

Poland

-

Portugal

Portugal

-

Puerto Rico

Puerto Rico

-

Qatar

Qatar

-

Republic of Moldova

Republic of Moldova

-

Rest of the United States

Rest of the United States

-

Réunion

Réunion

-

Reunion

Reunion

-

Romania

Romania

-

Rota (Northern Mariana Islands)

Rota (Northern Mariana Islands)

-

Russian

Russian

-

Russian Federation

Russian Federation

-

Rwanda

Rwanda

-

Saint Kitts and Nevis

Saint Kitts and Nevis

-

Saint Lucia

Saint Lucia

-

Saint Maarten (Dutch part)

Saint Maarten (Dutch part)

-

Saint Martin (French part)

Saint Martin (French part)

-

Saint Vincent and the Grenadines

Saint Vincent and the Grenadines

-

Saipan (Northern Mariana Islands)

Saipan (Northern Mariana Islands)

-

Samoa

Samoa

-

San Marino

San Marino

-

Saudi Arabia

Saudi Arabia

-

Senegal

Senegal

-

Serbia

Serbia

-

Seychelles

Seychelles

-

Sierra Leone

Sierra Leone

-

Singapore

Singapore

-

Slovakia

Slovakia

-

Slovenia

Slovenia

-

Solomon Islands

Solomon Islands

-

South Africa

South Africa

-

South Korea

South Korea

-

Spain

Spain

-

Sri Lanka

Sri Lanka

-

St. Kitts and Nevis

St. Kitts and Nevis

-

St. Maarten

St. Maarten

-

Suriname

Suriname

-

Swaziland (Eswatini)

Swaziland (Eswatini)

-

Sweden

Sweden

-

Switzerland

Switzerland

-

Syria

Syria

-

Taiwan

Taiwan

-

Taiwan, China

Taiwan, China

-

Tajikistan

Tajikistan

-

Tanzania

Tanzania

-

Thailand

Thailand

-

Tinian (Northern Mariana Islands)

Tinian (Northern Mariana Islands)

-

Togo

Togo

-

Tonga

Tonga

-

Trinidad and Tobago

Trinidad and Tobago

-

Tunisia

Tunisia

-

Turkey

Turkey

-

Turks and Caicos Islands

Turks and Caicos Islands

-

Uganda

Uganda

-

Ukraine

Ukraine

-

United Arab Emirates

United Arab Emirates

-

United Kingdom

United Kingdom

-

United Kingdom (Great Britain)

United Kingdom (Great Britain)

-

United States

United States

-

United States Virgin Islands

United States Virgin Islands

-

Uruguay

Uruguay

-

Utah

Utah

-

Uzbekistan

Uzbekistan

-

Vanuatu

Vanuatu

-

Venezuela

Venezuela

-

Vietnam

Vietnam

-

Wallis and Futuna

Wallis and Futuna

-

Washington

Washington

-

Yemen

Yemen

-

Zambia

Zambia

-

Zimbabwe

Zimbabwe

| Shipping method | Costs | Delivery Time | |

|---|---|---|---|

SF Express SF Express |

$21.08 | 6-8 business days |