FIRST ORDER

FREE 10% DISCOUNT

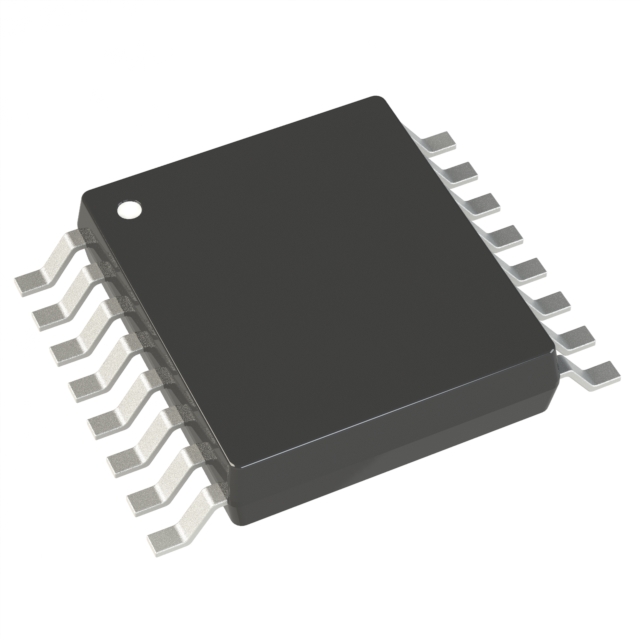

LOW VOLTAGE E2CMOS PLD GENERIC A

General Description

The NSC E²CMOS™ GAL人® devices combine a high per-formance CMOS process with electrically erasable floating

gate technology. This programmable memory technology applied to array logic provides designers with reconfigurable

logic and bipolar performance at significantly reduced pow-er levels.

The 24-pin GAL22V10 features 22 inputs, and 10 program-mable Output Logic Macro Cells (OLMCs) allowing each

TRI-STATE® output to be configured by the user. The archi-tecture of each output is user-programmable for registered

or combinatorial operation, active high or low polarity, and as an input, output or bidirectional I/O. This architecture

features variable product term distribution, from 8 to 16 logi-cal product terms to each output, as shown in the logic dia-

gram. CMOS circuitry allows the GAL22V10 to consume just 90 mA typical lcc which represents a 50% saving in power

when compared to its bipolar counterparts. Synchronous preset and asynchronous reset product terms have been

added which are common to all output registers to enhance system operation. The GAL22V10 is directly compatible

with the bipolar PAL22V10 in terms of functionality, fuse map, pinout, and electrical characteristics.

Programming is accomplished using industry standard avail-able hardware and software tools. NSC guarantees a mini-

mum 100 erase/write cycles.

Unique test circuitry and reprogrammable cells allow com-plete AC, DC, cell and functionality testing during manufac-

ture. Therefore, NSC guarantees 100% field programmabili-ty of all GAL devices. In addition, electronic signature is

available to provide positive device ID. A security circuit isbuilt-in, providing proprietary designs with copy protection.

Features

High performance E²CMOS technology

-15 ns maximum propagation delay

-fmax = 45 MHz with feedback

-TTL compatible 16 mA outputs

-UltraMOS® Ill advanced CMOS technology

-Internal pull-up resistor on all pins

Electrically erasable cell technology

-Reconfigurable logic

-Reprogrammable cells

-100% tested/guaranteed 100% yields

-High speed electrical erasure(<50 ms)

-20 year data retention

Ten output logic macrocells

-Maximum Flexibility

-Programmable output polarity

-Maximum flexibility for complex logic designs

-Full function/fuse map/parametric compatibility with PAL22V10 devices

Variable product term distribution

-From 8 to 16 product terms per output data function

Globai synchronous preset and asynchronous reset

Preload and power-up reset of all registers

-100% functional testability

Fully supported by National OPAL™ and OPALjr development software

Security cell prevents copying logic

How to choose FPGA for your project?

Hot Sales

Pricing And ODER

Stock:

0

Price:

$4.99

Quantity:

Shipping Cost

$28.63

PostNL International Mail 11-33

?Unconfirmed payment orders may not be able to deliver the normal cancellation of the order, please communicate with the email to confirm before making the relevant payment ~ Attached email phone number The platform has the right to cancel the unconfirmed payment orders do not need to bear the responsibility of default.

Shipment Date

2025/04/02 PM

Delivery Date

5-10 business days

About Logistics:

?Shipping time will be determined according to the logistics time, there will be differences in the place please understand!

| Sub-Total | $4.99 |

| Shipping: | $28.63 |

| Total | $33.62 |

Please send RFQ , we will respond immediately.

Product:

-

Afghanistan

Afghanistan

-

Afghanistan

Afghanistan

-

Albania

Albania

-

Algeria

Algeria

-

American Samoa

American Samoa

-

Andorra

Andorra

-

Angola

Angola

-

Anguilla

Anguilla

-

Antigua & Barbuda

Antigua & Barbuda

-

Argentina

Argentina

-

Arizona

Arizona

-

Armenia

Armenia

-

Aruba

Aruba

-

Australia

Australia

-

Austria

Austria

-

Azerbaijan

Azerbaijan

-

Bahamas

Bahamas

-

Bahrain

Bahrain

-

Bangladesh

Bangladesh

-

Barbados

Barbados

-

Belarus

Belarus

-

Belgium

Belgium

-

Belize

Belize

-

Benin

Benin

-

Bermuda

Bermuda

-

Bhutan

Bhutan

-

Bolivia

Bolivia

-

Bonaire

Bonaire

-

Bosnia and Herzegovina

Bosnia and Herzegovina

-

Botswana

Botswana

-

Brazil

Brazil

-

British Virgin Islands

British Virgin Islands

-

Brunei

Brunei

-

Bulgaria

Bulgaria

-

Burkina Faso

Burkina Faso

-

Burundi

Burundi

-

California

California

-

Cambodia

Cambodia

-

Cameroon

Cameroon

-

Canada

Canada

-

Cape Verde

Cape Verde

-

Cayman Islands

Cayman Islands

-

Central African Republic

Central African Republic

-

Chad

Chad

-

Chile

Chile

-

Colombia

Colombia

-

Colorado

Colorado

-

Congo

Congo

-

Cook Islands

Cook Islands

-

Costa Rica

Costa Rica

-

Côte d'Ivoire

Côte d'Ivoire

-

Croatia

Croatia

-

Curaçao

Curaçao

-

Curacao

Curacao

-

Cyprus

Cyprus

-

Czech Republic

Czech Republic

-

Democratic Republic of Congo

Democratic Republic of Congo

-

Democratic Republic of the Congo

Democratic Republic of the Congo

-

Denmark

Denmark

-

Djibouti

Djibouti

-

Dominica

Dominica

-

Dominican Republic

Dominican Republic

-

East Timor

East Timor

-

Ecuador

Ecuador

-

Egypt

Egypt

-

El Salvador

El Salvador

-

Eritrea

Eritrea

-

Estonia

Estonia

-

Eswatini

Eswatini

-

Ethiopia

Ethiopia

-

Faroe Islands

Faroe Islands

-

Fiji

Fiji

-

Finland

Finland

-

France

France

-

French Guiana

French Guiana

-

French Polynesia

French Polynesia

-

Gabon

Gabon

-

Gambia

Gambia

-

Georgia

Georgia

-

Germany

Germany

-

Ghana

Ghana

-

Gibraltar

Gibraltar

-

Greece

Greece

-

Greenland

Greenland

-

Grenada

Grenada

-

Guadeloupe

Guadeloupe

-

Guam

Guam

-

Guatemala

Guatemala

-

Guinea

Guinea

-

Guyana

Guyana

-

Haiti

Haiti

-

Honduras

Honduras

-

Hong Kong

Hong Kong

-

Hong Kong, China

Hong Kong, China

-

Hungary

Hungary

-

Iceland

Iceland

-

Idaho

Idaho

-

India

India

-

Indonesia

Indonesia

-

Iraq

Iraq

-

Ireland

Ireland

-

Israel

Israel

-

Italy

Italy

-

Ivory Coast

Ivory Coast

-

Jamaica

Jamaica

-

Japan

Japan

-

Jordan

Jordan

-

Kazakhstan

Kazakhstan

-

Kenya

Kenya

-

Kuwait

Kuwait

-

Kyrgyzstan

Kyrgyzstan

-

Laos

Laos

-

Latvia

Latvia

-

Lebanon

Lebanon

-

Lesotho

Lesotho

-

Liberia

Liberia

-

Libya

Libya

-

Liechtenstein

Liechtenstein

-

Liechtenstein (Switzerland)

Liechtenstein (Switzerland)

-

Lithuania

Lithuania

-

Luxembourg

Luxembourg

-

Macao, China

Macao, China

-

Macau

Macau

-

Macedonia

Macedonia

-

Madagascar

Madagascar

-

Malawi

Malawi

-

Malaysia

Malaysia

-

Maldives

Maldives

-

Mali

Mali

-

Malta

Malta

-

Marshall Islands

Marshall Islands

-

Martinique

Martinique

-

Mauritania

Mauritania

-

Mauritius

Mauritius

-

Mexico

Mexico

-

Micronesia

Micronesia

-

Moldova

Moldova

-

Monaco

Monaco

-

Monaco (France)

Monaco (France)

-

Mongolia

Mongolia

-

Montenegro

Montenegro

-

Montserrat

Montserrat

-

Morocco

Morocco

-

Mozambique

Mozambique

-

Myanmar

Myanmar

-

Namibia

Namibia

-

Nepal

Nepal

-

Netherlands

Netherlands

-

Netherlands Antilles

Netherlands Antilles

-

Nevada

Nevada

-

New Caledonia

New Caledonia

-

New Zealand

New Zealand

-

Nicaragua

Nicaragua

-

Niger

Niger

-

Nigeria

Nigeria

-

North Macedonia

North Macedonia

-

Northern Mariana Islands

Northern Mariana Islands

-

Norway

Norway

-

Oman

Oman

-

Oregon

Oregon

-

Other States in US

Other States in US

-

Pakistan

Pakistan

-

Palau

Palau

-

Palestinian Authority

Palestinian Authority

-

Palestinian Territories

Palestinian Territories

-

Panama

Panama

-

Papua New Guinea

Papua New Guinea

-

Paraguay

Paraguay

-

Peru

Peru

-

Philippines

Philippines

-

Poland

Poland

-

Portugal

Portugal

-

Puerto Rico

Puerto Rico

-

Qatar

Qatar

-

Republic of Moldova

Republic of Moldova

-

Rest of the United States

Rest of the United States

-

Réunion

Réunion

-

Reunion

Reunion

-

Romania

Romania

-

Rota (Northern Mariana Islands)

Rota (Northern Mariana Islands)

-

Russian

Russian

-

Russian Federation

Russian Federation

-

Rwanda

Rwanda

-

Saint Kitts and Nevis

Saint Kitts and Nevis

-

Saint Lucia

Saint Lucia

-

Saint Maarten (Dutch part)

Saint Maarten (Dutch part)

-

Saint Martin (French part)

Saint Martin (French part)

-

Saint Vincent and the Grenadines

Saint Vincent and the Grenadines

-

Saipan (Northern Mariana Islands)

Saipan (Northern Mariana Islands)

-

Samoa

Samoa

-

San Marino

San Marino

-

Saudi Arabia

Saudi Arabia

-

Senegal

Senegal

-

Serbia

Serbia

-

Seychelles

Seychelles

-

Sierra Leone

Sierra Leone

-

Singapore

Singapore

-

Slovakia

Slovakia

-

Slovenia

Slovenia

-

Solomon Islands

Solomon Islands

-

South Africa

South Africa

-

South Korea

South Korea

-

Spain

Spain

-

Sri Lanka

Sri Lanka

-

St. Kitts and Nevis

St. Kitts and Nevis

-

St. Maarten

St. Maarten

-

Suriname

Suriname

-

Swaziland (Eswatini)

Swaziland (Eswatini)

-

Sweden

Sweden

-

Switzerland

Switzerland

-

Syria

Syria

-

Taiwan

Taiwan

-

Taiwan, China

Taiwan, China

-

Tajikistan

Tajikistan

-

Tanzania

Tanzania

-

Thailand

Thailand

-

Tinian (Northern Mariana Islands)

Tinian (Northern Mariana Islands)

-

Togo

Togo

-

Tonga

Tonga

-

Trinidad and Tobago

Trinidad and Tobago

-

Tunisia

Tunisia

-

Turkey

Turkey

-

Turks and Caicos Islands

Turks and Caicos Islands

-

Uganda

Uganda

-

Ukraine

Ukraine

-

United Arab Emirates

United Arab Emirates

-

United Kingdom

United Kingdom

-

United Kingdom (Great Britain)

United Kingdom (Great Britain)

-

United States

United States

-

United States Virgin Islands

United States Virgin Islands

-

Uruguay

Uruguay

-

Utah

Utah

-

Uzbekistan

Uzbekistan

-

Vanuatu

Vanuatu

-

Venezuela

Venezuela

-

Vietnam

Vietnam

-

Wallis and Futuna

Wallis and Futuna

-

Washington

Washington

-

Yemen

Yemen

-

Zambia

Zambia

-

Zimbabwe

Zimbabwe

| Shipping method | Costs | Delivery Time | |

|---|---|---|---|

SF Express SF Express |

$21.08 | 6-8 business days |