FIRST ORDER

FREE 10% DISCOUNT

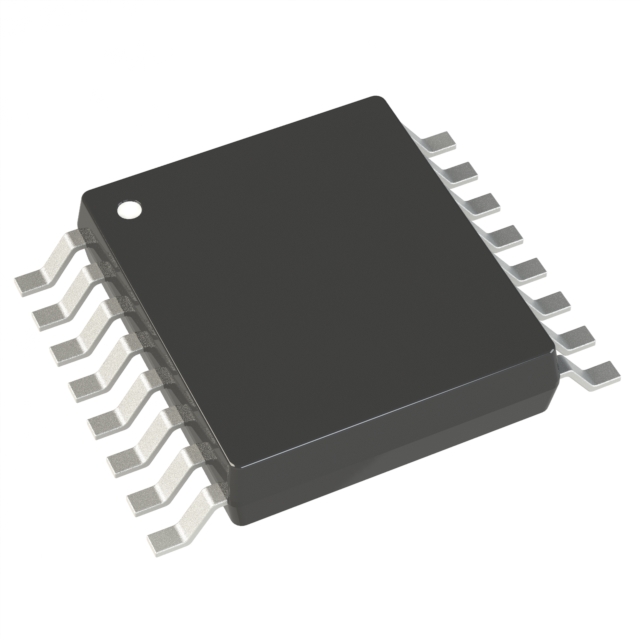

A Comprehensive Guide To MC56F8025MLD Microcontroller IC 16-Bit 32MHz 32KB (16K x 16) FLASH 44-LQFP (10x10)

Payment and disbursement

56800E 56F8xxx Microcontroller IC 16-Bit 32MHz 32KB (16K x 16) FLASH 44-LQFP (10x10)

56F8033/56F8023 Description

The 56F8033/56F8023 is a member of the 56800E core-based family of Digital Signal Controllers

(DSCs). It combines, on a single chip, the processing power of a DSP and the functionality of a

microcontroller with a flexible set of peripherals to create an extremely cost-effective solution. Because

of its low cost, configuration flexibility, and compact program code, the 56F8033/56F8023 is well-suited

for many applications. The 56F8033/56F8023 includes many peripherals that are especially useful for

industrial control, motion control, home appliances, general-purpose inverters, smart sensors, fire and

security systems, switched-mode power supply, power management, and medical monitoring

applications.

The 56800E core is based on a dual Harvard-style architecture consisting of three execution units

operating in parallel, allowing as many as six operations per instruction cycle. The MCU-style

programming model and optimized instruction set allow straightforward generation of efficient, compact

DSP and control code. The instruction set is also highly efficient for C compilers to enable rapid

development of optimized control applications.

The 56F8033/56F8023 supports program execution from internal memories. Two data operands can be

accessed from the on-chip data RAM per instruction cycle. The 56F8033/56F8023 also offers up to 26

General-Purpose Input/Output (GPIO) lines, depending on peripheral configuration.

The 56F8033 Digital Signal Controller includes 64KB of Program Flash and 8KB of Unified

Data/Program RAM. The 56F8023 Digital Signal Controller includes 32KB of Program Flash and 4KB of

Unified Data/Program RAM. Program Flash memory can be independently bulk erased or erased in pages.

Program Flash page erase size is 512 Bytes (256 Words).

56F8033/56F8023 Features

Digital Signal Controller Core

• Efficient 16-bit 56800E family Digital Signal Controller (DSC) engine with dual Harvard architecture

• As many as 32 Million Instructions Per Second (MIPS) at 32MHz core frequency

• Single-cycle 16 × 16-bit parallel Multiplier-Accumulator (MAC)

• Four 36-bit accumulators, including extension bits

• 32-bit arithmetic and logic multi-bit shifter

• Parallel instruction set with unique DSP addressing modes

• Hardware DO and REP loops

• Three internal address buses

• Four internal data buses

• Instruction set supports both DSP and controller functions

• Controller-style addressing modes and instructions for compact code

• Efficient C compiler and local variable support

• Software subroutine and interrupt stack with depth limited only by memory

• JTAG/Enhanced On-Chip Emulation (OnCE) for unobtrusive, processor speed-independent, real-time

debugging

Hot Sales

Pricing And ODER

Stock:

0

Price:

$0

Quantity:

Shipping Cost

$28.63

PostNL International Mail 11-33

?Unconfirmed payment orders may not be able to deliver the normal cancellation of the order, please communicate with the email to confirm before making the relevant payment ~ Attached email phone number The platform has the right to cancel the unconfirmed payment orders do not need to bear the responsibility of default.

Shipment Date

2025/04/21 AM

Delivery Date

5-10 business days

About Logistics:

?Shipping time will be determined according to the logistics time, there will be differences in the place please understand!

| Sub-Total | $0 |

| Shipping: | $28.63 |

| Total | $28.63 |

Please send RFQ , we will respond immediately.

Product:

-

Afghanistan

Afghanistan

-

Afghanistan

Afghanistan

-

Albania

Albania

-

Algeria

Algeria

-

American Samoa

American Samoa

-

Andorra

Andorra

-

Angola

Angola

-

Anguilla

Anguilla

-

Antigua & Barbuda

Antigua & Barbuda

-

Argentina

Argentina

-

Arizona

Arizona

-

Armenia

Armenia

-

Aruba

Aruba

-

Australia

Australia

-

Austria

Austria

-

Azerbaijan

Azerbaijan

-

Bahamas

Bahamas

-

Bahrain

Bahrain

-

Bangladesh

Bangladesh

-

Barbados

Barbados

-

Belarus

Belarus

-

Belgium

Belgium

-

Belize

Belize

-

Benin

Benin

-

Bermuda

Bermuda

-

Bhutan

Bhutan

-

Bolivia

Bolivia

-

Bonaire

Bonaire

-

Bosnia and Herzegovina

Bosnia and Herzegovina

-

Botswana

Botswana

-

Brazil

Brazil

-

British Virgin Islands

British Virgin Islands

-

Brunei

Brunei

-

Bulgaria

Bulgaria

-

Burkina Faso

Burkina Faso

-

Burundi

Burundi

-

California

California

-

Cambodia

Cambodia

-

Cameroon

Cameroon

-

Canada

Canada

-

Cape Verde

Cape Verde

-

Cayman Islands

Cayman Islands

-

Central African Republic

Central African Republic

-

Chad

Chad

-

Chile

Chile

-

Colombia

Colombia

-

Colorado

Colorado

-

Congo

Congo

-

Cook Islands

Cook Islands

-

Costa Rica

Costa Rica

-

Côte d'Ivoire

Côte d'Ivoire

-

Croatia

Croatia

-

Curaçao

Curaçao

-

Curacao

Curacao

-

Cyprus

Cyprus

-

Czech Republic

Czech Republic

-

Democratic Republic of Congo

Democratic Republic of Congo

-

Democratic Republic of the Congo

Democratic Republic of the Congo

-

Denmark

Denmark

-

Djibouti

Djibouti

-

Dominica

Dominica

-

Dominican Republic

Dominican Republic

-

East Timor

East Timor

-

Ecuador

Ecuador

-

Egypt

Egypt

-

El Salvador

El Salvador

-

Eritrea

Eritrea

-

Estonia

Estonia

-

Eswatini

Eswatini

-

Ethiopia

Ethiopia

-

Faroe Islands

Faroe Islands

-

Fiji

Fiji

-

Finland

Finland

-

France

France

-

French Guiana

French Guiana

-

French Polynesia

French Polynesia

-

Gabon

Gabon

-

Gambia

Gambia

-

Georgia

Georgia

-

Germany

Germany

-

Ghana

Ghana

-

Gibraltar

Gibraltar

-

Greece

Greece

-

Greenland

Greenland

-

Grenada

Grenada

-

Guadeloupe

Guadeloupe

-

Guam

Guam

-

Guatemala

Guatemala

-

Guinea

Guinea

-

Guyana

Guyana

-

Haiti

Haiti

-

Honduras

Honduras

-

Hong Kong

Hong Kong

-

Hong Kong, China

Hong Kong, China

-

Hungary

Hungary

-

Iceland

Iceland

-

Idaho

Idaho

-

India

India

-

Indonesia

Indonesia

-

Iraq

Iraq

-

Ireland

Ireland

-

Israel

Israel

-

Italy

Italy

-

Ivory Coast

Ivory Coast

-

Jamaica

Jamaica

-

Japan

Japan

-

Jordan

Jordan

-

Kazakhstan

Kazakhstan

-

Kenya

Kenya

-

Kuwait

Kuwait

-

Kyrgyzstan

Kyrgyzstan

-

Laos

Laos

-

Latvia

Latvia

-

Lebanon

Lebanon

-

Lesotho

Lesotho

-

Liberia

Liberia

-

Libya

Libya

-

Liechtenstein

Liechtenstein

-

Liechtenstein (Switzerland)

Liechtenstein (Switzerland)

-

Lithuania

Lithuania

-

Luxembourg

Luxembourg

-

Macao, China

Macao, China

-

Macau

Macau

-

Macedonia

Macedonia

-

Madagascar

Madagascar

-

Malawi

Malawi

-

Malaysia

Malaysia

-

Maldives

Maldives

-

Mali

Mali

-

Malta

Malta

-

Marshall Islands

Marshall Islands

-

Martinique

Martinique

-

Mauritania

Mauritania

-

Mauritius

Mauritius

-

Mexico

Mexico

-

Micronesia

Micronesia

-

Moldova

Moldova

-

Monaco

Monaco

-

Monaco (France)

Monaco (France)

-

Mongolia

Mongolia

-

Montenegro

Montenegro

-

Montserrat

Montserrat

-

Morocco

Morocco

-

Mozambique

Mozambique

-

Myanmar

Myanmar

-

Namibia

Namibia

-

Nepal

Nepal

-

Netherlands

Netherlands

-

Netherlands Antilles

Netherlands Antilles

-

Nevada

Nevada

-

New Caledonia

New Caledonia

-

New Zealand

New Zealand

-

Nicaragua

Nicaragua

-

Niger

Niger

-

Nigeria

Nigeria

-

North Macedonia

North Macedonia

-

Northern Mariana Islands

Northern Mariana Islands

-

Norway

Norway

-

Oman

Oman

-

Oregon

Oregon

-

Other States in US

Other States in US

-

Pakistan

Pakistan

-

Palau

Palau

-

Palestinian Authority

Palestinian Authority

-

Palestinian Territories

Palestinian Territories

-

Panama

Panama

-

Papua New Guinea

Papua New Guinea

-

Paraguay

Paraguay

-

Peru

Peru

-

Philippines

Philippines

-

Poland

Poland

-

Portugal

Portugal

-

Puerto Rico

Puerto Rico

-

Qatar

Qatar

-

Republic of Moldova

Republic of Moldova

-

Rest of the United States

Rest of the United States

-

Réunion

Réunion

-

Reunion

Reunion

-

Romania

Romania

-

Rota (Northern Mariana Islands)

Rota (Northern Mariana Islands)

-

Russian

Russian

-

Russian Federation

Russian Federation

-

Rwanda

Rwanda

-

Saint Kitts and Nevis

Saint Kitts and Nevis

-

Saint Lucia

Saint Lucia

-

Saint Maarten (Dutch part)

Saint Maarten (Dutch part)

-

Saint Martin (French part)

Saint Martin (French part)

-

Saint Vincent and the Grenadines

Saint Vincent and the Grenadines

-

Saipan (Northern Mariana Islands)

Saipan (Northern Mariana Islands)

-

Samoa

Samoa

-

San Marino

San Marino

-

Saudi Arabia

Saudi Arabia

-

Senegal

Senegal

-

Serbia

Serbia

-

Seychelles

Seychelles

-

Sierra Leone

Sierra Leone

-

Singapore

Singapore

-

Slovakia

Slovakia

-

Slovenia

Slovenia

-

Solomon Islands

Solomon Islands

-

South Africa

South Africa

-

South Korea

South Korea

-

Spain

Spain

-

Sri Lanka

Sri Lanka

-

St. Kitts and Nevis

St. Kitts and Nevis

-

St. Maarten

St. Maarten

-

Suriname

Suriname

-

Swaziland (Eswatini)

Swaziland (Eswatini)

-

Sweden

Sweden

-

Switzerland

Switzerland

-

Syria

Syria

-

Taiwan

Taiwan

-

Taiwan, China

Taiwan, China

-

Tajikistan

Tajikistan

-

Tanzania

Tanzania

-

Thailand

Thailand

-

Tinian (Northern Mariana Islands)

Tinian (Northern Mariana Islands)

-

Togo

Togo

-

Tonga

Tonga

-

Trinidad and Tobago

Trinidad and Tobago

-

Tunisia

Tunisia

-

Turkey

Turkey

-

Turks and Caicos Islands

Turks and Caicos Islands

-

Uganda

Uganda

-

Ukraine

Ukraine

-

United Arab Emirates

United Arab Emirates

-

United Kingdom

United Kingdom

-

United Kingdom (Great Britain)

United Kingdom (Great Britain)

-

United States

United States

-

United States Virgin Islands

United States Virgin Islands

-

Uruguay

Uruguay

-

Utah

Utah

-

Uzbekistan

Uzbekistan

-

Vanuatu

Vanuatu

-

Venezuela

Venezuela

-

Vietnam

Vietnam

-

Wallis and Futuna

Wallis and Futuna

-

Washington

Washington

-

Yemen

Yemen

-

Zambia

Zambia

-

Zimbabwe

Zimbabwe

| Shipping method | Costs | Delivery Time | |

|---|---|---|---|

SF Express SF Express |

$21.08 | 6-8 business days |