FIRST ORDER

FREE 10% DISCOUNT

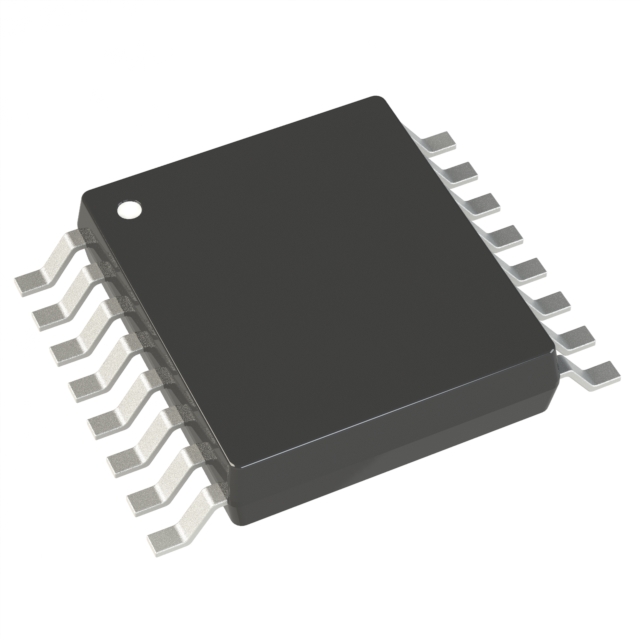

| Parameters | |

|---|---|

| Mfr | Efinix, Inc. |

| Series | Trion® |

| Package | Tray |

| Product Status | Active |

| Digi-Key Programmable | Not Verified |

| Number of Logic Elements/Cells | 19728 |

| Total RAM Bits | 1044 |

| Number of I/O | 97 |

| Voltage - Supply | 1.15V ~ 1.25V |

| Mounting Type | Surface Mount |

| Operating Temperature | 0°C ~ 85°C (TJ) |

| Package / Case | 144-LQFP |

| Supplier Device Package | 144-LQFP (20x20) |

Trion® Field Programmable Gate Array (FPGA) IC 97 1044 19728 144-LQFP

Description

The T20 FPGA features the high-density, low-power Efinix® Quantum™ architecture

wrapped with an I/O interface for easy integration. With a high I/O to logic ratio and

differential I/O support, T20 FPGAs supports a variety of applications that need wide

I/O connectivity. The T20 also includes a MIPI D-PHY with a built-in, royalty-free

CSI-2 controller, which is the most popular camera interface used in the mobile industry.

Additionally, T20 FPGAs support a DDR3, LPDDR3, LPDDR2 PHY with memory

controller hard IP that provides faster access to data stored in memory. The carefully tailored

combination of core resources and I/O provides enhanced capability for applications such as

embedded vision, voice and gesture recognition, intelligent sensor hubs, power management,

and LED drivers.

Features

• High-density, low-power Quantum™ architecture

• Built on SMIC 40 nm process

• Core leakage current as low as 6.8 mA(1)

• FPGA interface blocks

— GPIO

— PLL

— LVDS 800 Mbps per lane with up to 20 TX pairs and 26 RX pairs

— MIPI DPHY with CSI-2 controller hard IP, 1.5 Gbps per lane

— DDR3, LPDDR3, LPDDR2 x16 PHY with memory controller hard IP, 12.8 Gbps aggregate bandwidth

• Programmable high-performance I/O

— Supports 1.8, 2.5, and 3.3 V single-ended I/O standards and interfaces

• Flexible on-chip clocking

— 16 low-skew global clock signals can be driven from off-chip external clock signals or PLL synthesized clock signals

— PLL support

• Flexible device configuration

— Standard SPI interface (active, passive, and daisy chain)

— JTAG interface

— Optional Mask Programmable Memory (MPM) capability

• Fully supported by the Efinity® software, an RTL-to-bitstream compiler

How to choose FPGA for your project?

Hot Sales

Pricing And ODER

Stock:

0

Price:

$12.06

Quantity:

Shipping Cost

$28.63

PostNL International Mail 11-33

?Unconfirmed payment orders may not be able to deliver the normal cancellation of the order, please communicate with the email to confirm before making the relevant payment ~ Attached email phone number The platform has the right to cancel the unconfirmed payment orders do not need to bear the responsibility of default.

Shipment Date

2025/04/03 AM

Delivery Date

5-10 business days

About Logistics:

?Shipping time will be determined according to the logistics time, there will be differences in the place please understand!

| Sub-Total | $12.06 |

| Shipping: | $28.63 |

| Total | $40.69 |

Please send RFQ , we will respond immediately.

Product:

-

Afghanistan

Afghanistan

-

Afghanistan

Afghanistan

-

Albania

Albania

-

Algeria

Algeria

-

American Samoa

American Samoa

-

Andorra

Andorra

-

Angola

Angola

-

Anguilla

Anguilla

-

Antigua & Barbuda

Antigua & Barbuda

-

Argentina

Argentina

-

Arizona

Arizona

-

Armenia

Armenia

-

Aruba

Aruba

-

Australia

Australia

-

Austria

Austria

-

Azerbaijan

Azerbaijan

-

Bahamas

Bahamas

-

Bahrain

Bahrain

-

Bangladesh

Bangladesh

-

Barbados

Barbados

-

Belarus

Belarus

-

Belgium

Belgium

-

Belize

Belize

-

Benin

Benin

-

Bermuda

Bermuda

-

Bhutan

Bhutan

-

Bolivia

Bolivia

-

Bonaire

Bonaire

-

Bosnia and Herzegovina

Bosnia and Herzegovina

-

Botswana

Botswana

-

Brazil

Brazil

-

British Virgin Islands

British Virgin Islands

-

Brunei

Brunei

-

Bulgaria

Bulgaria

-

Burkina Faso

Burkina Faso

-

Burundi

Burundi

-

California

California

-

Cambodia

Cambodia

-

Cameroon

Cameroon

-

Canada

Canada

-

Cape Verde

Cape Verde

-

Cayman Islands

Cayman Islands

-

Central African Republic

Central African Republic

-

Chad

Chad

-

Chile

Chile

-

Colombia

Colombia

-

Colorado

Colorado

-

Congo

Congo

-

Cook Islands

Cook Islands

-

Costa Rica

Costa Rica

-

Côte d'Ivoire

Côte d'Ivoire

-

Croatia

Croatia

-

Curaçao

Curaçao

-

Curacao

Curacao

-

Cyprus

Cyprus

-

Czech Republic

Czech Republic

-

Democratic Republic of Congo

Democratic Republic of Congo

-

Democratic Republic of the Congo

Democratic Republic of the Congo

-

Denmark

Denmark

-

Djibouti

Djibouti

-

Dominica

Dominica

-

Dominican Republic

Dominican Republic

-

East Timor

East Timor

-

Ecuador

Ecuador

-

Egypt

Egypt

-

El Salvador

El Salvador

-

Eritrea

Eritrea

-

Estonia

Estonia

-

Eswatini

Eswatini

-

Ethiopia

Ethiopia

-

Faroe Islands

Faroe Islands

-

Fiji

Fiji

-

Finland

Finland

-

France

France

-

French Guiana

French Guiana

-

French Polynesia

French Polynesia

-

Gabon

Gabon

-

Gambia

Gambia

-

Georgia

Georgia

-

Germany

Germany

-

Ghana

Ghana

-

Gibraltar

Gibraltar

-

Greece

Greece

-

Greenland

Greenland

-

Grenada

Grenada

-

Guadeloupe

Guadeloupe

-

Guam

Guam

-

Guatemala

Guatemala

-

Guinea

Guinea

-

Guyana

Guyana

-

Haiti

Haiti

-

Honduras

Honduras

-

Hong Kong

Hong Kong

-

Hong Kong, China

Hong Kong, China

-

Hungary

Hungary

-

Iceland

Iceland

-

Idaho

Idaho

-

India

India

-

Indonesia

Indonesia

-

Iraq

Iraq

-

Ireland

Ireland

-

Israel

Israel

-

Italy

Italy

-

Ivory Coast

Ivory Coast

-

Jamaica

Jamaica

-

Japan

Japan

-

Jordan

Jordan

-

Kazakhstan

Kazakhstan

-

Kenya

Kenya

-

Kuwait

Kuwait

-

Kyrgyzstan

Kyrgyzstan

-

Laos

Laos

-

Latvia

Latvia

-

Lebanon

Lebanon

-

Lesotho

Lesotho

-

Liberia

Liberia

-

Libya

Libya

-

Liechtenstein

Liechtenstein

-

Liechtenstein (Switzerland)

Liechtenstein (Switzerland)

-

Lithuania

Lithuania

-

Luxembourg

Luxembourg

-

Macao, China

Macao, China

-

Macau

Macau

-

Macedonia

Macedonia

-

Madagascar

Madagascar

-

Malawi

Malawi

-

Malaysia

Malaysia

-

Maldives

Maldives

-

Mali

Mali

-

Malta

Malta

-

Marshall Islands

Marshall Islands

-

Martinique

Martinique

-

Mauritania

Mauritania

-

Mauritius

Mauritius

-

Mexico

Mexico

-

Micronesia

Micronesia

-

Moldova

Moldova

-

Monaco

Monaco

-

Monaco (France)

Monaco (France)

-

Mongolia

Mongolia

-

Montenegro

Montenegro

-

Montserrat

Montserrat

-

Morocco

Morocco

-

Mozambique

Mozambique

-

Myanmar

Myanmar

-

Namibia

Namibia

-

Nepal

Nepal

-

Netherlands

Netherlands

-

Netherlands Antilles

Netherlands Antilles

-

Nevada

Nevada

-

New Caledonia

New Caledonia

-

New Zealand

New Zealand

-

Nicaragua

Nicaragua

-

Niger

Niger

-

Nigeria

Nigeria

-

North Macedonia

North Macedonia

-

Northern Mariana Islands

Northern Mariana Islands

-

Norway

Norway

-

Oman

Oman

-

Oregon

Oregon

-

Other States in US

Other States in US

-

Pakistan

Pakistan

-

Palau

Palau

-

Palestinian Authority

Palestinian Authority

-

Palestinian Territories

Palestinian Territories

-

Panama

Panama

-

Papua New Guinea

Papua New Guinea

-

Paraguay

Paraguay

-

Peru

Peru

-

Philippines

Philippines

-

Poland

Poland

-

Portugal

Portugal

-

Puerto Rico

Puerto Rico

-

Qatar

Qatar

-

Republic of Moldova

Republic of Moldova

-

Rest of the United States

Rest of the United States

-

Réunion

Réunion

-

Reunion

Reunion

-

Romania

Romania

-

Rota (Northern Mariana Islands)

Rota (Northern Mariana Islands)

-

Russian

Russian

-

Russian Federation

Russian Federation

-

Rwanda

Rwanda

-

Saint Kitts and Nevis

Saint Kitts and Nevis

-

Saint Lucia

Saint Lucia

-

Saint Maarten (Dutch part)

Saint Maarten (Dutch part)

-

Saint Martin (French part)

Saint Martin (French part)

-

Saint Vincent and the Grenadines

Saint Vincent and the Grenadines

-

Saipan (Northern Mariana Islands)

Saipan (Northern Mariana Islands)

-

Samoa

Samoa

-

San Marino

San Marino

-

Saudi Arabia

Saudi Arabia

-

Senegal

Senegal

-

Serbia

Serbia

-

Seychelles

Seychelles

-

Sierra Leone

Sierra Leone

-

Singapore

Singapore

-

Slovakia

Slovakia

-

Slovenia

Slovenia

-

Solomon Islands

Solomon Islands

-

South Africa

South Africa

-

South Korea

South Korea

-

Spain

Spain

-

Sri Lanka

Sri Lanka

-

St. Kitts and Nevis

St. Kitts and Nevis

-

St. Maarten

St. Maarten

-

Suriname

Suriname

-

Swaziland (Eswatini)

Swaziland (Eswatini)

-

Sweden

Sweden

-

Switzerland

Switzerland

-

Syria

Syria

-

Taiwan

Taiwan

-

Taiwan, China

Taiwan, China

-

Tajikistan

Tajikistan

-

Tanzania

Tanzania

-

Thailand

Thailand

-

Tinian (Northern Mariana Islands)

Tinian (Northern Mariana Islands)

-

Togo

Togo

-

Tonga

Tonga

-

Trinidad and Tobago

Trinidad and Tobago

-

Tunisia

Tunisia

-

Turkey

Turkey

-

Turks and Caicos Islands

Turks and Caicos Islands

-

Uganda

Uganda

-

Ukraine

Ukraine

-

United Arab Emirates

United Arab Emirates

-

United Kingdom

United Kingdom

-

United Kingdom (Great Britain)

United Kingdom (Great Britain)

-

United States

United States

-

United States Virgin Islands

United States Virgin Islands

-

Uruguay

Uruguay

-

Utah

Utah

-

Uzbekistan

Uzbekistan

-

Vanuatu

Vanuatu

-

Venezuela

Venezuela

-

Vietnam

Vietnam

-

Wallis and Futuna

Wallis and Futuna

-

Washington

Washington

-

Yemen

Yemen

-

Zambia

Zambia

-

Zimbabwe

Zimbabwe

| Shipping method | Costs | Delivery Time | |

|---|---|---|---|

SF Express SF Express |

$21.08 | 6-8 business days |

PDF

PDF